# **Kit Contents**

Each kit has the following items:

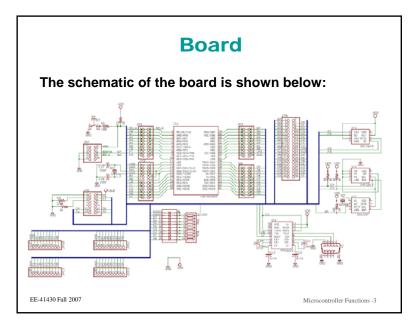

- Board with microcontroller (18(L)F4620)

- Power brick for the board.

- Programmer, and power brick for programmer.

- USB logic analyzer

- Digital Volt Meter.

- Serial cable

EE-41430 Fall 2007

• Needle nose and cutting pliers.

# <section-header><section-header><section-header><section-header><section-header><section-header><list-item><list-item><list-item><list-item><list-item><list-item>

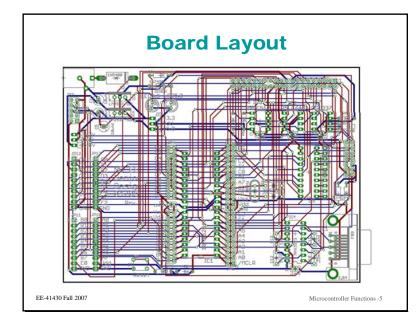

# **Board Features**

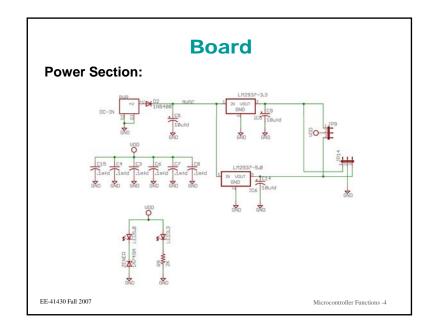

The board has 2 voltage regulators on it, and you can select to run the processor at either 3.3 or 5.0 volts. (LCD gets 5 volts in any case.)

Your board might have either an 18LF4620 or an 18F4620.

Note: Only the 18LF4620 will run at 3.3 volts.

The processor has a simple program in it, which writes to the LCD display, blinks the lights, and then exercises the serial port.

EE-41430 Fall 2007

Microcontroller Functions -7

# Notes

Some of these boards were built by students in previous years. No guarantees.

The programmer connection to the board may or may not be keyed to prevent incorrect connections. The edge of the connector towards you is painted gold or silver. Incorrectly connecting the programmer has the nasty habit of blowing very small transistors on the board. I have replacements, but you will be doing the repairs.

You should plan on ordering free sample microcontrollers from Microchip, before you do something that destroys the one you have.

EE-41430 Fall 2007

# **Notes**

The power brick used for the microcontroller board is cheap and unregulated. Don't expect the voltage you get to be the voltage on the slide switch.

You will want about 7 volts out of the power brick. (In one of the tasks, you will determine why.) You should use the meter to find the lowest setting of the slide switch that gives you about 7 volts.

There is a polarity switch on the power brick. It should be to the left.

```

EE-41430 Fall 2007

```

Microcontroller Functions -9

the board. This is far easier then the little clips. Do not remove the leads from the logic analyzer to use for jumpers. They are expensive (\$60 to replace the set), and I lost too many in the past. (If

I see you doing this, you will loose your logic analyzer and it is a very useful tool.)

EE-41430 Fall 2007

Microcontroller Functions -10

# Why this processor? This processor is overkill for most projects. (More memory and features than necessary.) It makes a lot of sense to use a processor with excess capacity to develop your prototype. (Why?)

EE-41430 Fall 2007

| Configu                                                                                             | uration Bits                                    |

|-----------------------------------------------------------------------------------------------------|-------------------------------------------------|

| bits or fuses that are<br>These are bits that can<br>running of the progra<br>the device is program | e set within the programmer ompiler directives. |

| EE-41430 Fall 2007                                                                                  | Microcontroller Functions -17                   |

| Configu                                                                                             | uration Bits                                    |

#### These bits are set in pragma directives:

#pragma DATA 0x300001, \_OSC\_HS\_1H // HS osc #pragma DATA 0x300003, \_WDT\_OFF\_2H // wdt off #pragma DATA 0x300006, \_LVP\_OFF\_4L // lvp off #pragma DATA \_CONFIG3H, \_MCLRE\_ON\_3H //enable mclr

These are using definitions found in the system.h include file.

| EE-41430 Fa | all 2007 |

|-------------|----------|

|-------------|----------|

Microcontroller Functions -19

# **Configuration Bits**

Configuration bits control a number of things and are discussed under "Special Features of the CPU" in the documentation.

| File             | Name      | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3                | Bit 2   | Bit 1  | Bit 0  | Default/<br>Unprogrammee<br>Value |

|------------------|-----------|-------|-------|-------|--------|----------------------|---------|--------|--------|-----------------------------------|

| 300001h          | CONFIG1H  | IESO  | FCMEN | -     | -      | FOSC3                | FOSC2   | FOSC1  | FOSCO  | 00 0111                           |

| 300002h          | CONFIG2L  | _     | -     | _     | BORV1  | BORV0                | BOREN1  | BOREN0 | PWRTEN | 1 1111                            |

| 300003h          | CONFIG2H  | -     | -     | -     | WDTPS3 | WDTPS2               | WDTPS1  | WDTPS0 | WDTEN  | 1 1111                            |

| 300005h          | CONFIG3H  | MCLRE | -     | -     | -      | -                    | LPT10SC | PBADEN | CCP2MX | 1011                              |

| 300006h          | CONFIG4L  | DEBUG | XINST | -     | -      | -                    | LVP     | -      | STVREN | 101-1                             |

| 300008h          | CONFIG5L  | -     | -     | -     | -      | CP3(1)               | CP2     | CP1    | CP0    | 1111                              |

| 300009h          | CONFIG5H  | CPD   | CPB   | -     | -      | -                    | -       | _      | -      | 11                                |

| 30000Ah          | CONFIG6L  | -     | -     | -     | -      | WRT3(1)              | WRT2    | WRT1   | WRT0   | 1111                              |

| 30000Bh          | CONFIG6H  | WRTD  | WRTB  | WRTC  | -      | -                    | -       | -      | -      | 111                               |

| 30000Ch          | CONFIG7L  | -     | -     | -     | -      | EBTR3 <sup>(1)</sup> | EBTR2   | EBTR1  | EBTR0  | 1111                              |

| 30000Dh          | CONFIG7H  | -     | EBTRB | -     | -      | -                    | -       | -      | -      | -1                                |

| 3FFFF <b>E</b> h | DEVID1(1) | DEV2  | DEV1  | DEV0  | REV4   | REV3                 | REV2    | REV1   | REV0   | XXXX XXXX                         |

| 3FFFFFh          | DEVID2(1) | DEV10 | DEV9  | DEV6  | DEV7   | DEVô                 | DEV5    | DEV4   | DEV3   | 0000 1100                         |

| TARIE 23-1- | CONFIGURATION BITS AND DEVICE IDE |

|-------------|-----------------------------------|

| Configuration Bits                                                                                               |                                                                                                                                            |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| The location of the confi                                                                                        | g register is defines:                                                                                                                     |  |  |  |  |

| <pre>#define _CONFIG1H #define _CONFIG2L #define _CONFIG2H #define _CONFIG3H #define _CONFIG4L</pre>             | 0x00300001<br>0x00300002<br>0x00300003<br>0x00300005<br>0x00300006                                                                         |  |  |  |  |

| Various bit in the resiste                                                                                       | ers are defined also:                                                                                                                      |  |  |  |  |

| #define _OSC_HS_IH<br>#define _OSC_RC_1H<br>#define _OSC_EC_1H<br>#define _OSC_ECIO6_1H<br>#define _OSC_HSPLL_1H | 0x000000F2 // RS<br>0x000000F3 // RC<br>0x000000F4 // EC-OSC2 as Clock Out<br>0x000000F5 // EC-OSC2 as RA6<br>0x000000F6 // HS-PLL Enabled |  |  |  |  |

| EE-41430 Fall 2007                                                                                               | Microcontroller Functions -20                                                                                                              |  |  |  |  |

|           | <b>Configuration Bits</b>                                                                                           |                                                              |

|-----------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| То        | turn off the watch dog timer:                                                                                       | l recommend                                                  |

| #pr<br>or | ragma DATA 0x300003, _WDT_OFF_2H                                                                                    | <ul> <li>Turn off<br/>want to u</li> <li>Turn off</li> </ul> |

|           | cagma DATA _CONFIG2H, _WDT_OFF_2H                                                                                   | The boar<br>on them.<br>dependir                             |

|           | set the oscillator to high speed and multiply the crystal speed by 4:                                               | In addition, t<br>frequency                                  |

| #pra      | agma DATA 0x300001, _OSC_HSPLL_1H //40 mhz                                                                          | #pragma                                                      |

|           | ngs like the latter should be done advisedly, because the<br>18LF4620 will not operate at 40 MHz at lower voltages. | This directiv<br>in delay ro<br>how fast t                   |

EE-41430 Fall 2007

Microcontroller Functions -21

# **Configuration Bits**

nd that you:

- the watch dog timer, until you are sure that you use it.

- low voltage programming

- ards that you will be using have 10MHz crystals n. You should set the oscillator to HS or HSPLL, ing on the desired speed.

there is a pragma for the clock

**V**:

na CLOCK\_FREQ 1000000

ve is necessary if you use any of the built routines, as the program needs to know the clock is.

EE-41430 Fall 2007

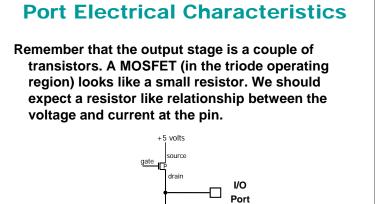

# **Port Electrical Characteristics**

When connecting things to ports, we are concerned with the current and voltage at the pins.

The electrical spec specifies:

- $V_{IH}$  Voltage that will be interpreted as high on an input.

- V<sub>II</sub> Voltage that will be interpreted as low on an input

- $V_{OH}$  Voltage on the pin in the output high state.

- V<sub>OL</sub> Voltage on the pin in the output low state.

- I<sub>OH</sub> Current a pin will source in the high output state.

- I<sub>OL</sub> Current a pin will sink in the low output state.

Note that as inputs, the impedance is very high, and thus there is very little current into the device. This is called "leakage" current and is on the order of 1µA.

Microcontroller Functions -24

| h.              |                                     |                                                              | ·                                                                       |

|-----------------|-------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------|

| U rumm          | ig at 5.0 volts, ti                 | iese ale the                                                 | values.                                                                 |

| V <sub>IH</sub> | minimum                             | 2.0 volts                                                    |                                                                         |

| VIL             | maximum                             | 0.8 volts                                                    |                                                                         |

| ļ               | lh.<br>20 runnin<br>V <sub>IH</sub> | h.<br>20 running at 5.0 volts, th<br>V <sub>IH</sub> minimum | V running at 5.0 volts, these are the V <sub>IH</sub> minimum 2.0 volts |

EE-41430 Fall 2007

Microcontroller Functions -25

# **Port Electrical Characteristics**

26.3 DC Characteristics: PIC18F2525/2620/4525/4620 (Industrial) PIC18LF2525/2620/4525/4620 (Industrial)

| Param<br>No.   | Symbol | Characteristic               | Min                | Max        | Units | Conditions                        |

|----------------|--------|------------------------------|--------------------|------------|-------|-----------------------------------|

|                | VIL    | Input Low Voltage            |                    |            |       |                                   |

|                |        | I/O ports:                   |                    |            |       |                                   |

| D030           |        | with TTL buffer              | Vss                | 0.15 VDD   | V     | VDD < 4.5V                        |

| D030A          |        |                              | -                  | 0.8        | V     | $4.5V \le VDD \le 5.5V$           |

| D031           |        | with Schmitt Trigger buffer  | Vss                | 0.2 VDD    | V     |                                   |

| D032           |        | MCLR                         | Vss                | 0.2 VDD    | V     |                                   |

| D033           |        | OSC1                         | Vss                | 0.3 VDD    | V     | HS, HSPLL modes                   |

| D033A          |        | OSC1                         | Vss                | 0.2 VDD    | V     | RC, EC modes <sup>(1)</sup>       |

| D033B          |        | OSC1                         | Vss                | 0.3 VDD    | V V   | XT, LP modes                      |

| 0034           |        | T13CKI                       | Vss                | 0.3 VDD    | V     |                                   |

|                | ViH    | Input High Voltage           |                    |            |       |                                   |

| D040           | 1      | VO ports:<br>with TTL buffer | 0.25 Vpp + 0.8V    | Vpp        | ) v   | Vpp < 4.5V                        |

| D040A          |        | with IIL buffer              | 2.0                | VDD        | 1 v   | 4.5V < Vpp < 5.5V                 |

| D040A          |        | with Schmitt Trigger buffer  | 0.8 Vpp            | VDD        | v     | 4.5V ≤ VDD ≤ 5.5V                 |

|                |        |                              |                    |            | -     |                                   |

| D042           |        | MCLR                         | 0.8 VDD            | VDD        | V     |                                   |

| 0043           |        | OSC1                         | 0.7 Vpp            | VDD        | V     | HS, HSPLL modes                   |

| D043A<br>D043B |        | OSC1<br>OSC1                 | 0.8 VDD<br>0.9 VDD | VDD<br>VDD | V.    | EC mode<br>RC mode <sup>(1)</sup> |

| D043B          |        | OSC1                         | 1.6                | VDD        | l v   | XT, LP modes                      |

| D044           |        | T13CKI                       | 1.6                | Vpp        | v     | All, Er modes                     |

# **Port Electrical Characteristics**

Outputs aren't as easy, since we must consider both the voltage and the current. For example, if we short an output pin to ground, we shouldn't expect it to produce a "high" output voltage.

| V <sub>он</sub> | minimum | 4.3 volts | I <sub>он</sub> < -3 mA  |

|-----------------|---------|-----------|--------------------------|

| V <sub>oL</sub> | maximum | 0.6 volts | l <sub>oL</sub> < 8.5 mA |

The  $V_{OH}$  spec says a high output will be a minimum of 4.3 volts as long as the current out of the pin is less than 3 mA.

The  $V_{OL}$  spec says a low output will be a maximum of 0.6 volts as long as the current into the pin is less than 8.5 mA.

Note that current into the device is defined as positive.

#### EE-41430 Fall 2007

Microcontroller Functions -27

# **Port Electrical Characteristics**

26.3 DC Characteristics: PIC18F2525/2620/4525/4620 (Industrial) PIC18LF2525/2620/4525/4620 (Industrial) (Continued) Standard Operating Conditions (unless otherwise stated) DC CHARACTERISTICS Operating temperature -40°C ≤ TA ≤ +85°C for industrial Param Symbol Characteristic Min Max Conditions Units No. Output Low Voltage VOL D080 I/O ports 0.6 V IOL = 8.5 mA, VDD = 4.5V. \_ -40°C to +85°C D083 OSC2/CLKO 0.6 v IOL = 1.6 mA, VDD = 4.5V, \_ (RC, RCIO, EC, ECIO modes) -40°C to +85°C Output High Voltage<sup>(3)</sup> VOH D090 I/O ports VDD - 0.7 ٧ IOH = -3.0 mA, VDD = 4.5V, \_ -40°C to +85°C D092 OSC2/CLKO Vpp - 0.7 V IOH = -1.3 mA, VDD = 4.5V, \_

(RC, RCIO, EC, ECIO modes)

EE-41430 Fall 2007

-40°C to +85°C

# gate VO Port source Microcontroller Functions -29

# **Port Electrical Characteristics**

- In addition to sourcing 3.5 mA and sinking 8mA, there is also a restriction on the total current sourced or sunk by groups of I/O ports.

- Added together, the current sourced or sunk by all ports combined can't exceed 200 mA.

- The absolute maximum information is found in the device document.

EE-41430 Fall 2007

Microcontroller Functions -30

# **Port Electrical Characteristics**

#### 26.0 ELECTRICAL CHARACTERISTICS

#### Absolute Maximum Ratings<sup>(†)</sup>

EE-41430 Fall 2007

| -65°C to +150°C<br>-0.3V to (Vno + 0.3V)<br>-0.3V to +7.5V<br>0V to +13.25V<br> |

|---------------------------------------------------------------------------------|

| -0.3V to +7.5V<br>0V to +13.25V<br>.1.0W<br>.300 mA                             |

|                                                                                 |

|                                                                                 |

|                                                                                 |

|                                                                                 |

|                                                                                 |

|                                                                                 |

| ±20 mA                                                                          |

|                                                                                 |

|                                                                                 |

|                                                                                 |

|                                                                                 |

|                                                                                 |

|                                                                                 |

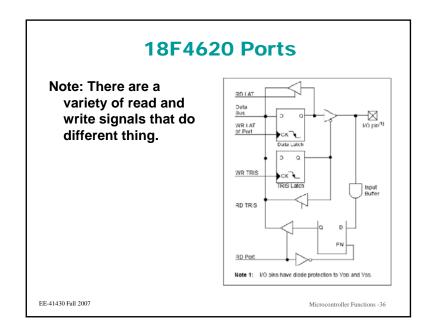

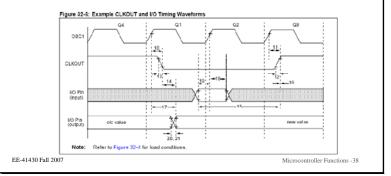

# **Basic I/O**

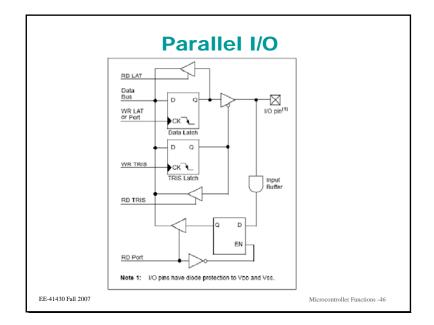

Note that the device does a read-modify-write. That means that the state of the port is first read, then it is modified, then it is reloaded into the register.

In some circumstances, this can cause issues if you are writing and immediately reading and the signal hasn't had a chance to settle.

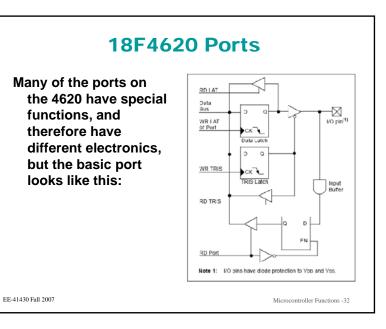

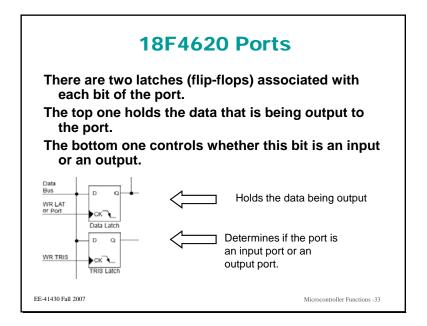

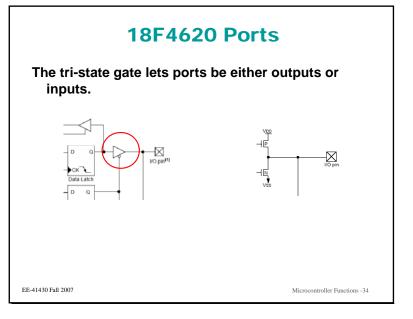

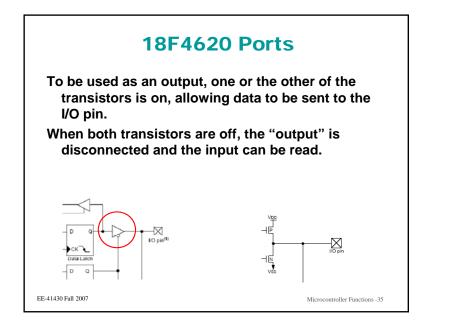

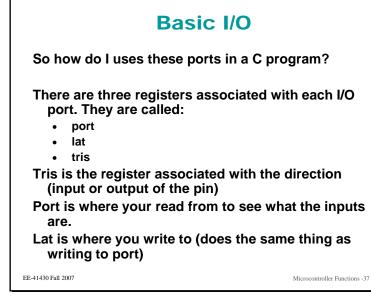

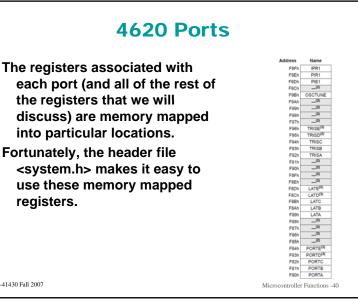

# **4620 Ports**The 4620 has:<br/> • 4 8-bit ports named a, b, c, and d.<br/> • One 3-bit port named e.The re<br/>each<br/>the re<br/>disc<br/>into<br/>registers:<br/> • porta<br/> • Itrisa<br/> • lataThe same is true, mutatis mutandis, for the other<br/>ports.EtterEtterEtter

| #define | PORTA | 0x00000F80 |

|---------|-------|------------|

| #define | PORTB | 0x00000F81 |

| #define | PORTC | 0x00000F82 |

| #define | PORTD | 0x00000F83 |

| #define | PORTE | 0x00000F84 |

| #define | LATA  | 0x00000F89 |

| #define | LATB  | 0x00000F8A |

| #define | LATC  | 0x00000F8B |

| #define | LATD  | 0x00000F8C |

| #define | LATE  | 0x00000F8D |

| #define | DDRA  | 0x00000F92 |

| #define | TRISA | 0x00000F92 |

| #define | DDRB  | 0x00000F93 |

| #define | TRISB | 0x00000F93 |

| #define | DDRC  | 0x00000F94 |

| #define |       | 0x00000F94 |

| #define | DDRD  | 0x00000F95 |

| #define |       | 0x00000F95 |

| #define | DDRE  | 0x00000F96 |

system.h

# system.h

The system.h file defines registers in lower case using

| v            | olatile | char | porta | @PORTA; |                               |

|--------------|---------|------|-------|---------|-------------------------------|

| v            | olatile | char | portb | @PORTB; |                               |

| v            | olatile | char | portc | @PORTC; |                               |

| v            | olatile | char | portd | @PORTD; |                               |

| v            | olatile | char | porte | @PORTE; |                               |

| v            | olatile | char | lata  | @LATA;  |                               |

| v            | olatile | char | latb  | @LATB;  |                               |

| v            | olatile | char | latc  | @LATC;  |                               |

| v            | olatile | char | latd  | @LATD;  |                               |

| v            | olatile | char | late  | @LATE;  |                               |

| v            | olatile | char | ddra  | @DDRA;  |                               |

| v            | olatile | char | trisa | @DDRA;  |                               |

| v            | olatile | char | ddrb  | @DDRB;  |                               |

| v            | olatile | char | trisb | @DDRB;  |                               |

| v            | olatile | char | ddrc  | @DDRC;  |                               |

| v            | olatile | char | trisc | @DDRC;  |                               |

| v            | olatile | char | ddrd  | @DDRD;  |                               |

| v            | olatile | char | trisd | @DDRD;  |                               |

| v            | olatile | char | ddre  | @DDRE;  |                               |

| v            | olatile | char | trise | @DDRE;  |                               |

|              |         |      |       |         |                               |

|              |         |      |       |         |                               |

| EE-41430 Fal | 11 2007 |      |       |         | Microcontroller Functions -42 |

|              |         |      |       |         |                               |

|              |         |      |       |         |                               |

EE-41430 Fall 2007

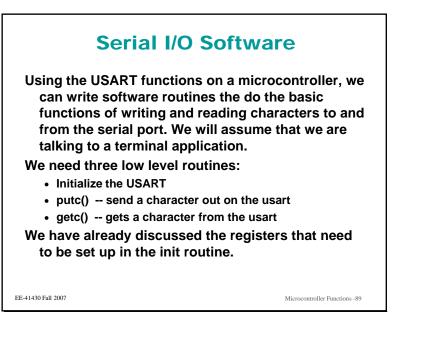

# Serial I/O

- One of the most common interfaces found on computers is the serial interface.

- Bytes of data are sent in a serial fashion, that is, one bit at a time.

- The standard for serial interface is called RS-232. It is used to send data over distances on the order of 25 feet.

- It is gradually being replaced in modern computers by the faster and more flexible USB (Universal Serial Bus) interface.

- RS-232 is still very common, very simple to implement, and well supported by software.

EE-41430 Fall 2007

# Serial I/O

There are several things that must be done to connect a microcontroller to a computer.

- You need an application running on the computer that can accept serial data. A commonly available application is HyperTerminal, which is a simple terminal emulation program that is standard software on all PC's.

- · Data sent between the microcontroller and the computer is sent using particular voltages (that are different from the standard voltages found on a microcontroller.) This requires level conversion.

- You need software in the microcontroller that will read and write serial data.

```

EE-41430 Fall 2007

```

EE-41430 Fall 2007

Microcontroller Functions -51

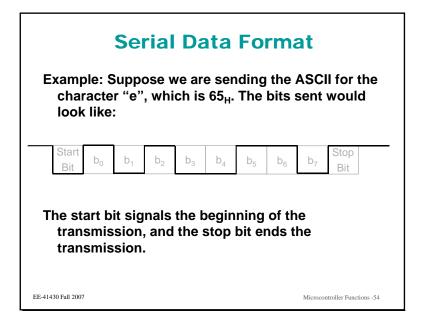

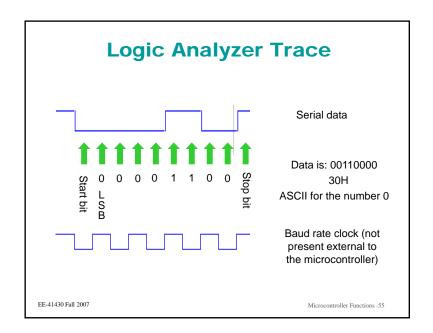

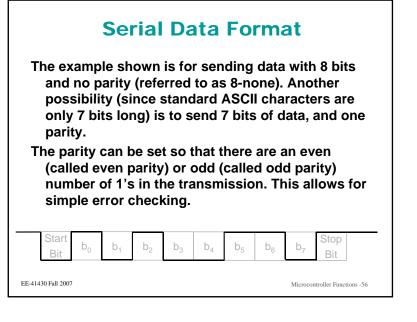

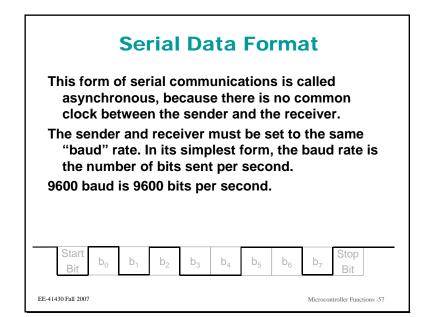

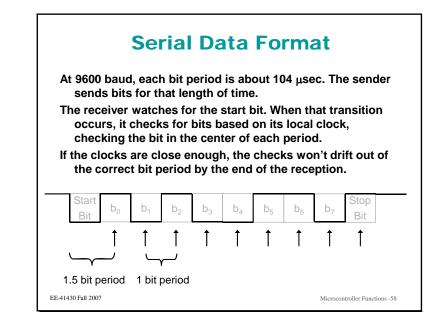

# Serial Data Format

If a data byte with the bits labeled  $b_7 - b_0$  is sent over a serial link, the format looks like this:

| Start<br>Bit | h              | h              | h              | h              | h              | h              | h              | h              | Stop |

|--------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|------|

| Bit          | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | b <sub>4</sub> | b <sub>5</sub> | D <sub>6</sub> | D <sub>7</sub> | Bit  |

The line is normally high, and the start bit begins a transmission by going low. Each bit of the byte being sent follows as a 1 or a 0. Finally, the stop bit is sent as a 1.

EE-41430 Fall 2007

| a dat<br>over | a by           | te wi          | th th          | e bits         | s lab          | Fo<br>eled I<br>t lool | b <sub>7</sub> – k | o <sub>o</sub> is |                              |

|---------------|----------------|----------------|----------------|----------------|----------------|------------------------|--------------------|-------------------|------------------------------|

| Start<br>Bit  | b <sub>0</sub> | b <sub>1</sub> | b <sub>2</sub> | b <sub>3</sub> | b <sub>4</sub> | b <sub>5</sub>         | b <sub>6</sub>     | b <sub>7</sub>    | Stop<br>Bit                  |

| tran:<br>bein | smis<br>g se   | sion           | by g<br>llows  | oing           | low.           | Each                   | ı bit o            | of the            | egins a<br>e byte<br>ne stop |

| is used.                                            |         |                           |                                                     |     |

|-----------------------------------------------------|---------|---------------------------|-----------------------------------------------------|-----|

|                                                     |         |                           |                                                     |     |

|                                                     |         |                           |                                                     |     |

| Modem Cable - Straigh                               | t Cable | DB9 to DB9                |                                                     |     |

| DTE Device (Computer)                               | DB9     | DTE to DCE<br>Connections | DCE Device (Modem)                                  | DB9 |

| Pin# DB9 RS-232 Signal Name                         | es      | Signal Direction          | Pin# DB9 RS-232 Signal Names                        | s   |

| #1 Carrier Detector (DCD)                           | CD      |                           | #1 Carrier Detector (DCD)                           | CD  |

| #2 Receive Data (Rx)                                | RD      | ∛                         | #2 Receive Data (Rx)                                | RD  |

| #3 Tran smit Data (Tx)                              | TD      |                           | #3 Transmit Data (Tx)                               | TD  |

| #4 Data Terminal Ready                              | DTR     |                           | #4 Data Terminal Ready                              | DTR |

| #5 Signal Ground/Common (SG)                        | GND     |                           | #5 Signal Ground/Common (SG)                        | GND |

| #6 Data Set Ready                                   | DSR     | <del> </del>              | #6 Data Set Ready                                   | DSR |

| #7 Request to Send                                  | RTS     |                           | #7 Request to Send                                  | RTS |

| #8 CleartoSend                                      | CTS     |                           | #8 Clear to Send                                    | CTS |

|                                                     |         |                           |                                                     |     |

| #9 Ring Indicator<br>Soldered to DB9 Metal - Shield | RI      |                           | #9 Ring Indicator<br>Soldered to DB9 Metal - Shield | RI  |

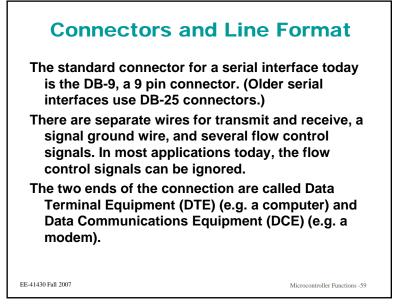

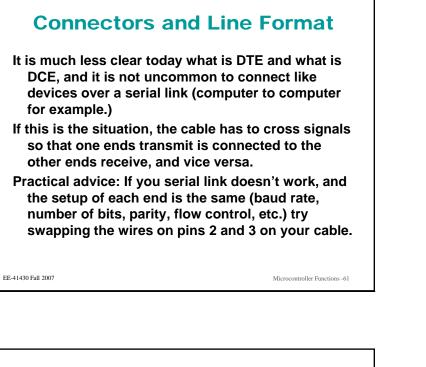

# **Connectors and Line Format**

- The actual signals sent are not 5 volt signals. RS-232 sends a negative voltage (typically -12 volts) to signify a "1" and a positive voltage (typically +12 volts) to signify a "0".

- This used to be a pain, because it meant that in addition to the 5 volt supply for you microcontroller, you needed a +12 and a -12 volt supply for the serial connection.

- Modern technology has come to the rescue with a device called the MAX232, which will take in a signal that is 0 or 5 volts and put out a signal that is +12 or -12 volts (using only a 5 volt supply!)

EE-41430 Fall 2007

Microcontroller Functions -62

# **The USART**

USART stands for Universal Synchronous Asynchronous Receiver transmitter. It is a hardware device built into computers and microcontrollers that accepts a byte from the computer and shifts the byte our serially, and accepts a serial set of bit and gives it to the computer in parallel.

There is a USART inside the 18F4620, and it is a common feature of microcontrollers. (Note that if your application calls for a serial connection, you should choose a microcontroller with a built in USART.)

EE-41430 Fall 2007

Microcontroller Functions -63

# **The USART**

- The USART greatly simplifies the task of serial communications. It is set up for the desired baud rate and number of bits, and then the microcontroller need only give it the byte to send, and the USART does the rest.

- On the receive side, the USART receives the serial bit stream and gives the corresponding byte to the microcontroller.

- In the 18F4620 USART, the transmitter and receiver are functionally separate, but share the same baud rate generator

EE-41430 Fall 2007

| tra                               | baud r<br>nsmit<br>ed to l | ted. E                            | Both (                           | ends                                 | •••••                             | e seri        | al co         |               |                           |

|-----------------------------------|----------------------------|-----------------------------------|----------------------------------|--------------------------------------|-----------------------------------|---------------|---------------|---------------|---------------------------|

| There                             | e are a                    | a nun                             | nber o                           | of sta                               | ndarc                             | l bau         | d rat         | es.           |                           |

| Tho H                             | baud r                     | ato ir                            | a the                            | 1854                                 | 620 ie                            | con           | trollo        | d by          | 2                         |

|                                   | -                          | -                                 | -                                |                                      | 020 13                            | COIL          | lione         | uby           | a                         |

| nu                                | mber                       | of reg                            | gister                           | 'S:                                  |                                   |               |               |               |                           |

|                                   |                            |                                   | -                                |                                      |                                   |               |               |               |                           |

| TABLE 18-                         | 2: REG                     | STERS A                           | SSOCIAT                          | ED WITH                              | BAUD RA                           | TE GENE       | RATOR         |               |                           |

| ADEE 10                           |                            |                                   |                                  |                                      |                                   |               |               |               | Reset Values              |

| Name                              | Bit 7                      | Bit 6                             | Bit 5                            | Bit 4                                | Bit 3                             | Bit 2         | Bit 1         | Bit 0         | on page                   |

|                                   | Bit 7<br>CSRC              | Bit 6<br>TX9                      | Bit 5<br>TXEN                    | Bit 4<br>SYNC                        | Bit 3<br>SENDB                    | Bit 2<br>BRGH | Bit 1<br>TRMT | Bit 0<br>TX9D |                           |

| Name<br>TXSTA                     |                            |                                   |                                  |                                      |                                   |               |               |               | on page                   |

| Name                              | CSRC<br>SPEN               | TX9                               | TXEN                             | SYNC                                 | SENDB                             | BRGH          | TRMT          | TX9D          | on page<br>51             |

| Name<br>TXSTA<br>RCSTA            | CSRC<br>SPEN               | TX9<br>RX9<br>RCIDL               | TXEN<br>SREN                     | SYNC<br>CREN<br>SCKP                 | SENDB<br>ADDEN<br>BRG16           | BRGH          | TRMT          | TX9D<br>RX9D  | on page<br>51<br>51       |

| Name<br>TXSTA<br>RCSTA<br>BAUDCON | CSRC<br>SPEN<br>ABDOVF     | TX9<br>RX9<br>RCIDL<br>aud Rate C | TXEN<br>SREN<br>—<br>Generator R | SYNC<br>CREN<br>SCKP<br>register Hig | SENDB<br>ADDEN<br>BRG16<br>h Byte | BRGH          | TRMT          | TX9D<br>RX9D  | on page<br>51<br>51<br>51 |

# Setting the Baud Rate

These table found in the documentation tell you how to set SPBRG for the desired baud rate.

There is often more than one choice for a given rate, so you should use the one with the smallest error.

| BAUD  | Fosc                  | = 40.000   | MHz                         | Fosc                  | = 20.000   | MHz                         | Fosc                  | = 10.00    | MHz                         | Fost                  | = 8.000    | MHz                         |

|-------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| (K)   | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3   | 0.300                 | 0.00       | 33332                       | 0.300                 | 0.00       | 16665                       | 0.300                 | 0.00       | 8332                        | 300                   | -0.01      | 6665                        |

| 1.2   | 1.200                 | 0.00       | 8332                        | 1.200                 | 0.02       | 4165                        | 1.200                 | 0.02       | 2082                        | 1200                  | -0.04      | 1665                        |

| 2.4   | 2.400                 | 0.02       | 4165                        | 2.400                 | 0.02       | 2082                        | 2.402                 | 0.06       | 1040                        | 2400                  | -0.04      | 832                         |

| 9.6   | 9.606                 | 0.06       | 1040                        | 9.596                 | -0.03      | 520                         | 9.615                 | 0.16       | 259                         | 9615                  | -0.16      | 207                         |

| 19.2  | 19.193                | -0.03      | 520                         | 19.231                | 0.16       | 259                         | 19.231                | 0.16       | 129                         | 19230                 | -0.16      | 103                         |

| 57.6  | 57.803                | 0.35       | 172                         | 57.471                | -0.22      | 86                          | 58.140                | 0.94       | 42                          | 57142                 | 0.79       | 34                          |

| 115.2 | 114.943               | -0.22      | 86                          | 116.279               | 0.94       | 42                          | 113.636               | -1.36      | 21                          | 117647                | -2.12      | 16                          |

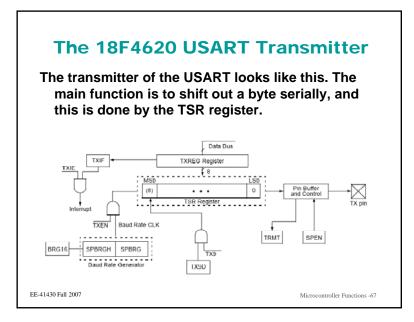

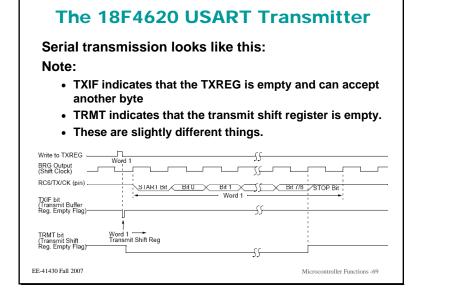

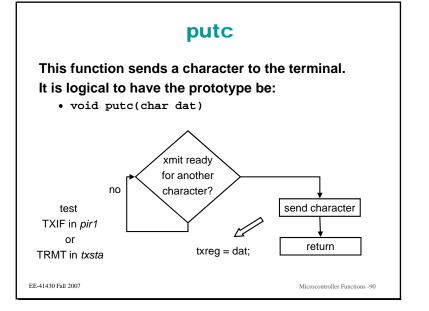

#### The 18F4620 USART Transmitter There are a number of interrupt flags, interrupt enables, and other bits that are associated with the transmitter: • TXEN – Transmitter Enable SPEN Serial Port Enable TXIF and TXIE – Transmit interrupt flag and enable • TRMT – Transmitter empty (MT) flag • RC6 – External pin on the 18F4620 Dala Bus TXREG Register TXIF **\$** 8 ... TSR Register TXEN Baud Rate CLM TRMT SPEN BRG16 SPRRGH SPRRG TX9D EE-41430 Fall 2007 Microcontroller Functions -68

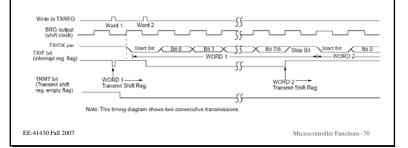

### The 18F4620 USART Transmitter

The difference between TRMT and TXIF can be seen by looking at back to back serial transmissions. The TXIF tells us that we can write another byte to be sent to TXREG. (Note that we can either of these flags, and don't have to use interrupts.)

# **18F4620 Transmitter Registers**

The registers involved with serial transmission are:

- SPBRGH and SPBRGL Get the correct value for the desired baud rate based on the system clock speed and BRGH.

- TXREG Location to place a byte to be transmitted out the serial port.

- TXSTA Transmitter status register.

- RCSAT Receiver status register. SPEN (serial port enable bit is found here.)

- PIE1 and PIR1 Peripheral Interrupt Enable register and Peripheral Interrupt Register (home to TXIE and TXIF respectively).

- INTCON Global interrupt enable and peripheral interrupt enable.

```

EE-41430 Fall 2007

```

Microcontroller Functions -71

# **18F4620 Transmitter Registers**

TABLE 18-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Name    | Bit 7                | Bit 6       | Bit 5       | Bit 4       | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|----------------------|-------------|-------------|-------------|-------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH             | PEIE/GIEL   | TMR0IE      | INTOIE      | RBIE  | TMR0IF | INTOIF | RBIF   | 49                         |

| PIR1    | PSPIF <sup>(1)</sup> | ADIF        | RCIF        | TXIE        | SSPIF | CCP1IF | TMR2IF | TMR1IF | 52                         |

| PIE1    | PSPIE <sup>(1)</sup> | ADIE        | RCIE        | TXIE        | SSPIE | CCP1IE | TMR2IE | TMR1IE | 52                         |

| IPR1    | PSPIP <sup>(1)</sup> | ADIP        | RCIP        | TXIP        | SSPIP | CCP1IP | TMR2IP | TMR1IP | 52                         |

| RCSTA   | SPEN                 | RX9         | SREN        | CREN        | ADDEN | FERR   | OERR   | RX9D   | 51                         |

| TXREG   | EUSART T             | ransmit Reg | ister       |             |       |        |        |        | 51                         |

| TXSTA   | CSRC                 | TX9         | TXEN        | SYNC        | SENDB | BRGH   | TRMT   | TX9D   | 51                         |

| BAUDCON | ABDOVF               | RCIDL       | _           | SCKP        | BRG16 | -      | WUE    | ABDEN  | 51                         |

| SPBRGH  | EUSART B             | aud Rate G  | enerator Re | gister High | Byte  |        |        |        | 51                         |

| SPBRG   | EUSART B             | aud Rate G  | enerator Re | gister Low  | Byte  |        |        |        | 51                         |

EE-41430 Fall 2007

|                | The main                                                                                                                                                                                                                        | -                                                                                                       |            |       |                                                                                                                                                  |                                                                                                          |                                          | 5 170           | , A.             |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------|------------------|

| ĸ              | EGISTER 10-1:                                                                                                                                                                                                                   | R/W-0                                                                                                   | R/W-0      | R/W-0 | R/W-0                                                                                                                                            |                                                                                                          | R/W-0                                    | R-1             | R/W-0            |

|                |                                                                                                                                                                                                                                 | CSRC                                                                                                    | TX9        | TXEN  | SYNC                                                                                                                                             | SENDB                                                                                                    | BRGH                                     | TRMT            | TX9D             |

|                |                                                                                                                                                                                                                                 | bit 7                                                                                                   |            |       |                                                                                                                                                  |                                                                                                          |                                          |                 | bit 0            |

| bit 6<br>bit 5 | Asynchronous mod<br>Don't care.<br>Synchronous mod<br>1 = Master mode (c)<br>0 = Slave mode (c)<br>TX9: 9-bit Transmi<br>1 = Selects 9-bit tr<br>0 = Selects 9-bit tr<br>TXEN: Transmit Ei<br>1 = Transmit disab<br>Note: SREN/ | E clock generated<br>lock from extensit<br>t Enable bit<br>ansmission<br>ansmission<br>nable bit<br>led | al source) | b     | 0 = Syn<br>Synchro<br>Don't ce<br>8 BRCH:<br>Asynchr<br>1 = H69'<br>0 = Low<br>Synchro<br>Unused<br>k1 TRMT: 1<br>= TSR<br>0 = TSR<br>k0 TX9D: 5 | High Baud Rate Select<br>speed<br>speed<br>nous.mode:<br>in this mode.<br>ransmit Shift Registe<br>empty | completed<br>ct bit<br>r Status bit<br>a | ared by hardwar | e upon completio |

#### **BAUDCON** register The BUADCON register is associated with both transmit and receive. REGISTER 18-3: BAUDCON: BAUD RATE CONTROL REGISTER R/W-0 R-1 U-0 R/W-0 R/W-0 U-0 R/W-0 R/W-0 ABDOVF RCIDL - SCKP BRG16 - WUE ABDEN bit 7 bit 0 ABDOVF: Auto-Baud Acquisition Rollover Status bit 3 BRC16: 16-bit Baud Rate Register Enable bit bit 7 1 = 16-bit Baud Rate Generator – SPBRGH and SPBRG 0 = 8-bit Baud Rate Generator – SPBRG only (Compatible mode), SF 1 = A BRG rollover has occurred during Auto-Baud I (must be cleared in software) bit 2 Unimplemented: Read as '0' n = No BRG rollover has occurred bit 1 WUE: Wake-up Enable bit bit 6 RCIDL: Receive Operation Idle Status bit Asynchronous mode: 1 = EUSART will continue to sample the RX pin - interrupt gener-1 = Receive operation is Idle cleared in hardware on following rising edge 0 = RX pin not monitored or rising edge detected 0 = Receive operation is active bit 5 Unimplemented: Read as '0' Synchronous mode: Unused in this mode. SCKP: Synchronous Clock Polarity Select bit bit 4 bit 0 ABDEN: Auto-Baud Detect Enable bit Asynchronous mode: Asynchronous.mode: 1 = Enable baud rate measurement on the next character. Requires Unused in this mode (55h); cleared in hardware upon completion Baud rate measurement disabled or completed Synchronous mode: 1 = Idle state for clock (CK) is a high level Synchronous mode: 0 = Idle state for clock (CK) is a low level Unused in this mode

# **Transmitter**

To setup the serial transmitter:

- Set SPBRGH and SPBRGL based on the system clock, and your choice of BRGH and BRG16.

- Set TXSTA for 8 bit asynchronous transmission with the correct value of BRGH.

- Set the correct values into the BAUDCON register.

- Enable the serial port (bit SPEN found in RXSTA)

#### To send serial data:

- Be sure that the TXREG is empty (either by polling TXIF or TRMT)

- Write the byte to be sent to TXREG.

| EE-41430 Fall 2007 |  |

|--------------------|--|

| EE-41430 Fall 2007 |  |

Microcontroller Functions -75

# **Transmitter and Interrupts**

The determination of whether to use interrupts for serial transmission depends on the application.

- Interrupts are most useful when you are sending a string of characters that you have already created. If this is the case, you can design your software to use the TXIF interrupt to load the next character in the string and send it.

- For many other applications, it is easier just to poll either TXIF or TRMT.

- If using interrupts, note that in addition to setting TXIE to enable the TXIF interrupt, you need to enable global interrupts (GIE) and also peripheral interrupts (PIE).

EE-41430 Fall 2007

EE-41430 Fall 2007

Microcontroller Functions -76

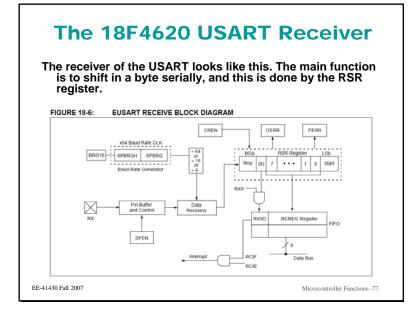

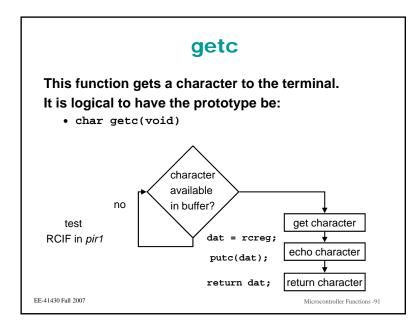

# The 18F4620 USART Receiver

The basic setup is the same as the transmitter.

- Baud rate is based on the same SPBRG value as the transmitter.

- · Data shifts in serially, and can be read from RCREG.

- Data comes in on external pin RC7.

- RCIE and RCIF are the Receiver Interrupt Enable and Receiver Interrupt flag respectively.

# The 18F4620 USART Receiver

The receiver is a little more complicated to deal with, for several reasons:

- When a byte is appears in the register is not under the control of the receiver, but depends on whatever is sending the data.

- The receiver must be able to detect bad things that might happen during transmission.

# The 18F4620 USART Receiver

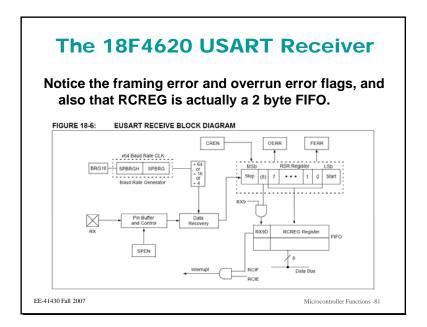

**Receiver Complications:**

- Since an external source is determining when bytes are sent, the microcontroller must be checking for data and reading it from the receiver, otherwise an error called and "overrun" will occur. This means that more bytes were received than can be held in the receiver for your program to read, and thus you missed some data.

- Almost every USART stops receiving data when this happens, and sets a flag (called the overrun error flag or OERR).

- If this occurs, you must reset the receiver to clear the error.

- To help this occur less frequently, the RCREG in the 18F4620 is a 2 byte FIFO (First In First Out) register that can hold to successive receptions.

- Another type of error that can be detected is a framing error, where the receiver doesn't find the stop bit where it is expected. (This often means a baud rate mismatch between transmitter and receiver.

```

EE-41430 Fall 2007

```

#### The 18F4620 USART Receiver The timing diagram: RX (pin) S Voit7/8/ STOP Rcv Shift Reg Rcv Buffer R Word 2 RCREG Word 1 RCREG Read Rcv Buffer Reg RCREG RCIF (Interrupt Flag OERR bit CREN This timing diagram shows three words appearing on the RX input. The RCREG (receive buffer) is read after the third word causing the OERR (overrun) bit to be set. Note: EE-41430 Fall 2007 Microcontroller Functions -82

# **18F4620 Receiver Registers**

The registers involved with serial reception are:

- SPBRGH and SPBRGL Gets the correct value for the desired baud rate based on the system clock speed and BRGH.

- RCREG 2 byte FIFO that hold the received data for reading by the microcontroller.

- RCSTA Receiver status register.

- TXSTA Home of BRGH

- PIE1 and PIR1 Peripheral Interrupt Enable register and Peripheral Interrupt Register (home to TXIE and TXIF respectively).

- INTCON Global interrupt enable (GIE) and peripheral interrupt enable (PIE).

# **18F4620 Receiver Registers**

#### TABLE 18-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Name    | Bit 7                | Bit 6         | Bit 5        | Bit 4        | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|----------------------|---------------|--------------|--------------|-------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH             | PEIE/GIEL     | TMROIE       | INTOIE       | RBIE  | TMR0IF | INTOIF | RBIF   | 49                         |

| PIR1    | PSPIF(1)             | ADIF          | RCIF         | TXIF         | SSPIF | CCP1IF | TMR2IF | TMR1IF | 52                         |

| PIE1    | PSPIE <sup>(1)</sup> | ADIE          | RCIE         | TXIE         | SSPIE | CCP1IE | TMR2IE | TMR1IE | 52                         |

| IPR1    | PSPIP <sup>(1)</sup> | ADIP          | RCIP         | TXIP         | SSPIP | CCP1IP | TMR2IP | TMR1IP | 52                         |

| RCSTA   | SPEN                 | RX9           | SREN         | CREN         | ADDEN | FERR   | OERR   | RX9D   | 51                         |

| RCREG   | EUSART F             | Receive Regis | ster         |              |       |        |        |        | 51                         |

| TXSTA   | CSRC                 | TX9           | TXEN         | SYNC         | SENDB | BRGH   | TRMT   | TX9D   | 51                         |

| BAUDCON | ABDOVF               | RCIDL         | -            | SCKP         | BRG16 | -      | WUE    | ABDEN  | 51                         |

| SPBRGH  | EUSART E             | aud Rate Ge   | nerator Re   | gister High  | Byte  |        |        |        | 51                         |

| SPBRG   | EUSART E             | aud Rate Ge   | enerator Res | gister Low B | Byte  |        |        |        | 51                         |

EE-41430 Fall 2007

EE-41430 Fall 2007

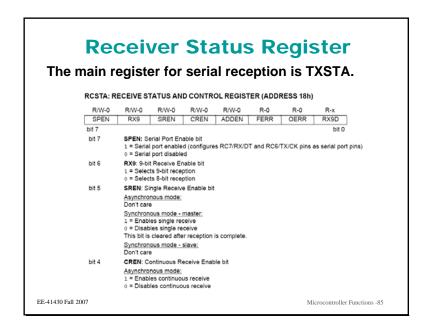

|       | n regis<br>Receive s'    |                          |              |               | •            | -             | XSTA.                |

|-------|--------------------------|--------------------------|--------------|---------------|--------------|---------------|----------------------|

| R/W-0 | R/W-0                    | R/W-0                    | R/W-0        | R/W-0         | R-0          | R-0           | R-x                  |

| SPEN  | RX9                      | SREN                     | CREN         | ADDEN         | FERR         | OERR          | RX9D                 |

| bit 7 |                          |                          |              |               |              |               | bit 0                |

| bit 3 | ADDEN: A                 | ddress Dete              | ct Enable b  | bit           |              |               |                      |

|       | Asynchrone               | ous mode 9-              | bit (RX9 =   | 1):           |              |               |                      |

|       |                          |                          | etection, en | ables interru | pt and load  | of the receiv | e buffer when        |

|       |                          | i> is set<br>s address d | etection all | bytes are re  | ceived and   | ninth hit ca  | n be used as parity  |

| bit 2 |                          | ming Error b             |              | bytes are re  | cerred, and  |               | r be used as party   |

|       |                          | g error (can             |              | by reading f  | RCREG reg    | ister and rec | eive next valid byte |

| bit 1 |                          | errun Error              |              |               |              |               |                      |

|       | 1 = Overru<br>0 = No ove |                          | be cleared   | by clearing b | it CREN)     |               |                      |

| bit O | RX9D: 9th                | bit of Recei             | ved Data (o  | an be parity  | bit, but mus | t be calculat | ed by user firmware  |

|       |                          |                          |              |               |              |               |                      |

|       |                          |                          |              |               |              |               |                      |

# <section-header><section-header><section-header><list-item><list-item><list-item><list-item><list-item><section-header>

# **Receiver and Interrupts**

The determination of whether to use interrupts for serial reception depends on the application, but it is often more advantageous in reception, since the microcontroller does not know when data is going to occur.

For some applications, it is easier just to poll either RCIF to see when data is available.

- It is wise to avoid turning on data reception until you are ready to handle it, otherwise overrun errors may occur.

- It is also wise to check for that error as part of your routine, particularly if you are polling RCIF.

- If using interrupts, note that in addition to setting RCIE to enable the RCIF interrupt, you need to enable global interrupts (GIE) and also peripheral interrupts (PIE).

```

EE-41430 Fall 2007

```

# Why Use Interrupts

Interrupts are most useful for events that happen asynchronously.

Suppose our project has a sensor that detects when the cup has been removed from the automatic drink dispenser. We could have our software in a look constantly checking this switch.

Often, however, there are other things that we need to be doing, so a better approach might be to use interrupts.

EE-41430 Fall 2007

Microcontroller Functions -98

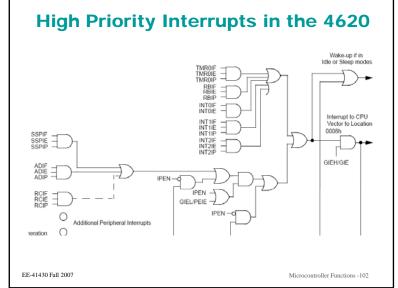

# **18F4620 Interrupts**

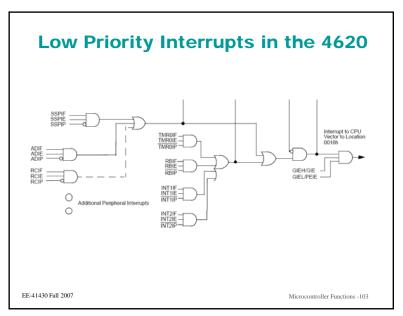

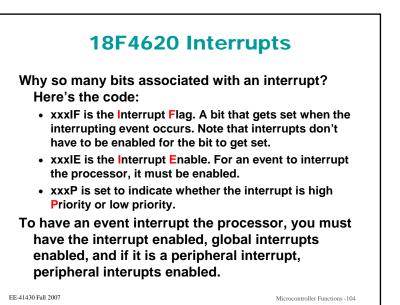

There are lots of things that can generate an interrupt on the 4620. These include events such as a timer turning over (counting from FFFF to 0000), a character arriving in the USART, etc.

There are also certain port bits that have interrupt functions associated with them so that an external event can cause the interrupt.

The interupts in this device are divided into two groups, regular interrupts and peripheral interrupts.

There is also now priority associated with the interrupts.

EE-41430 Fall 2007

Microcontroller Functions -99

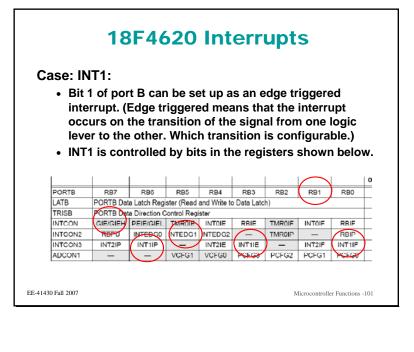

# **18F4620 Interrupts**

How do I know if the interrupt I want to use is peripheral or not? Read the damn manual! (oops, sorry!)

Case: USART receive:

- We saw that the RCIF (Receive interrupt flag) occurred when a character shows up in the usart.

- Looking at the manual, we can see that this is a peripheral interrupt because of the name of the register in which it lives and the requirement of PEIE (Peripheral interrupt enable) be set as can be seen in the manual.

| INTCON | GIE/GIEH             | PEIE/GIEL | TMR0IE | INT0IE | RBIE  | TMR0IF | INTOIF | RBIF   |

|--------|----------------------|-----------|--------|--------|-------|--------|--------|--------|

| PIR1   | PSPIF <sup>(1)</sup> | ADIF      | RCIF   | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF |

| PIE1   | PSPIE <sup>(1)</sup> | ADIE      | RCIE   | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE |

| IPR1   | PSPIP <sup>(1)</sup> | ADIP      | RCIP   | TXIP   | SSPIP | CCP1IP | TMR2IP | TMR1IP |

| RCSTA  | SPEN                 | RX9       | SREN   | CREN   | ADDEN | FERR   | OERR   | RX9D   |

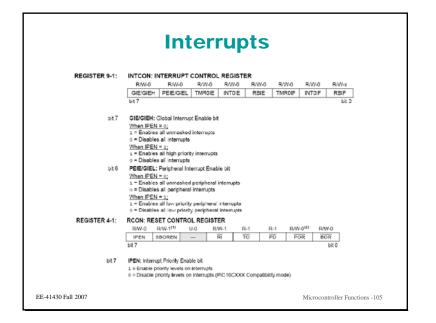

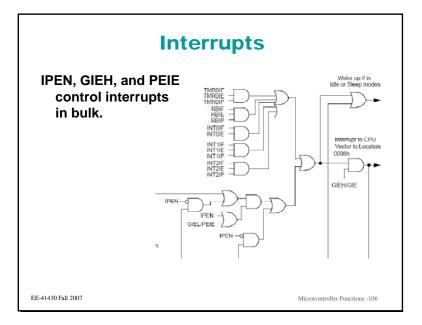

# Handling Interrupts in Software

There are several things you need to do to use an interrupt:

- Setup the particular hardware function to generate an interrupt.

- Enable that specific hardware interrupt to occur.

- · Enable interrupts in general to occur (GEI).

- Perhaps enable peripheral interrupts (PEIE)

- Set IPEN as desired.

- Write software to do what you need to do when the interrupt occurs

| 41430 Fall 2007 |

|-----------------|

|-----------------|

Microcontroller Functions -107

# Handling Interrupts in Software

There is a predefined function called interrupt which is declared:

void interrupt (void);

- Upon interrupt, the software execution switches from whatever it was doing, and executes this function. This works like any other function call, except it occurs asynchronously based on some hardware event, not because it was called by a line in your program.

- The interrupt routine should precede the main routine in your code.

```

EE-41430 Fall 2007

```

###

EE-41430 Fall 2007

**Generic Interrupt Routine** Note that I am using bit variables to make my life easier. I would define volatile bit rcif@pir1.5 volatile bit intlif@intcon3.1 : PIR1: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 1 R/W-0 R/W-0 R-0 R-0 R/W-0 R/W-0 R/W-0 R/W-0 PSPIF<sup>(1)</sup> ADIF RCIF TXIF SSPIF CCP1IF TMR2IF TMR1IF bit 7 bit 0 INTCON3: INTERRUPT CONTROL REGISTER 3 R/W-1 R/W-1 U-0 R/W-0 R/W-0 U-0 RAV-0 DAM-0 INT2IP INT1IP INT2IE INT1IE INT2IF INT1IF bit 7 bit 0 EE-41430 Fall 2007 Microcontroller Functions -111

# Generic Interrupt Routine

Microcontroller Functions -110

I may be strange but I think it is easier and produces more readable code if you do: if (rcif) // see if receive char interrupt { rcif = 0; // clear interrupt bit rather than if (pirl & 0x20) // see if receive char int { pirl &= 11011111b; // clear interrupt bit

# **Timer / Counters**

- A timer / counter is a register inside the microcontroller that increments.

- If it increments based on the system clock it is called a timer.

- If it increments based on some external signal, it is called a counter.

- As a timer, the register will allow you to determine how long an event was.

- As a counter, the register will allow you to determine how many events occurred.

# Suppose you are precisely positioning something via a motor turning a screw drive. An shaft encoder can give you a pulse for every n<sup>th</sup> of a turn the shaft makes. By counting these pulses, you can determine the position. Note that one of the functions related to timer/counters is a compare function, which can be combined with a counter to tell you when a particular value of the count is reached.

**Counter Application**

EE-41430 Fall 2007

Microcontroller Functions -115

EE-41430 Fall 2007

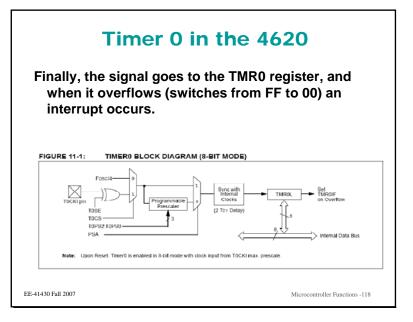

| Regi        | sters/E                     | Bits as   | ssoci    | ated v            | with t | imer 0 | ).     |       |                            |

|-------------|-----------------------------|-----------|----------|-------------------|--------|--------|--------|-------|----------------------------|

| ABLE 11     | -1: REGIS                   | STERS ASS | SOCIATED | WITH TH           | MERO   |        |        |       |                            |

| Name        | Bit 7                       | Bit 6     | Bit 5    | Bit 4             | Bit 3  | Bit 2  | Bit 1  | Bit 0 | Reset<br>Values<br>on page |

| MROL        | Timer0 Register Low Byte    |           |          |                   |        |        |        | 50    |                            |

| MROH        |                             |           |          |                   |        |        |        | 50    |                            |

| NTCON       | GIE/GIEH                    | PEIE/GIEL | TMR0IE   | INT0IE            | RBIE   | TMR0IF | INTOIF | RBIF  | 49                         |

| 0CON        | TMR0ON                      | T08BIT    | TOCS     | TOSE              | PSA    | T0PS2  | T0PS1  | T0PS0 | 50                         |

| INTC<br>R/W | <b>ON2: INTE</b><br>/-1 R/W |           |          | . REGIST<br>R/W-1 | U-0    | R/W-1  | U-0    | R/W   | /-1                        |

| RB          |                             | DGO INTE  | EDG1 IN  | TEDG2             | _      | TMR0IP | _      | RB    | IP                         |

|             |                             |           |          |                   |        |        |        |       | bit 0                      |

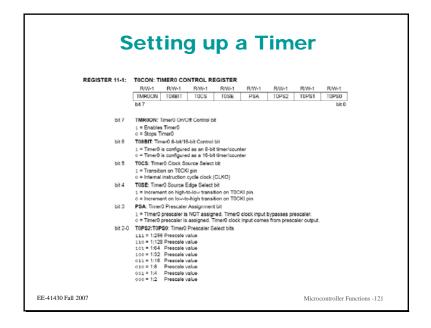

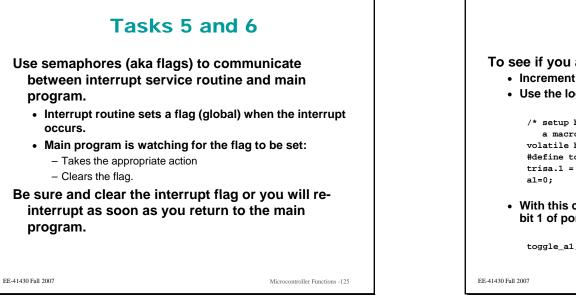

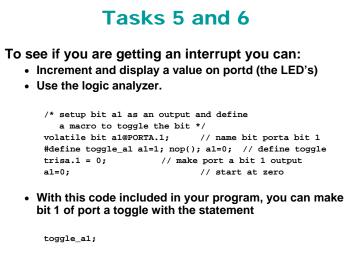

# Tasks 5 and 6

Tasks 5 and 6 involve timers and interrupts.

Task 5 starts with a single interrupt timer combination, with task 6 adding a second.

**Issues:**

- You will have to set up timer 0 to provide one interrupt per second. This involves getting the timer set up correctly, with the correct pre-scale and loading the correct value into the count register.

- Set all the bits correctly so that the processor can be interrupted.

- Limitations of the compiler.

Microcontroller Functions -123

# Tasks 5 and 6

The compiler does not allow you to call a function from two different execution threads. Thus, if you are using the LCD in the main program, you can't use it as part of your interrupt service routing.

You don't have to worry about using priority in the interrupts. The default is to have a single priority and that will work fine in tasks 5 and 6.

EE-41430 Fall 2007

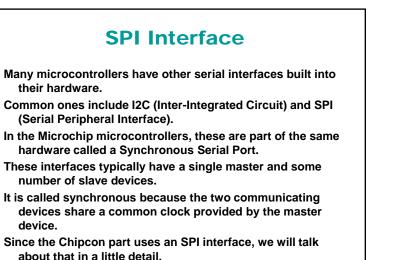

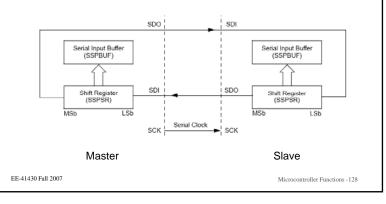

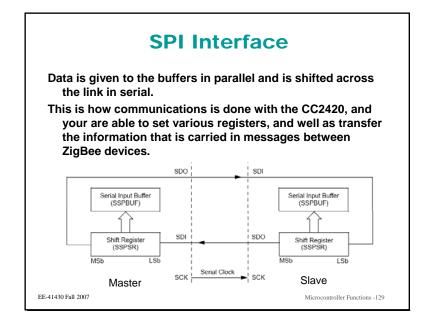

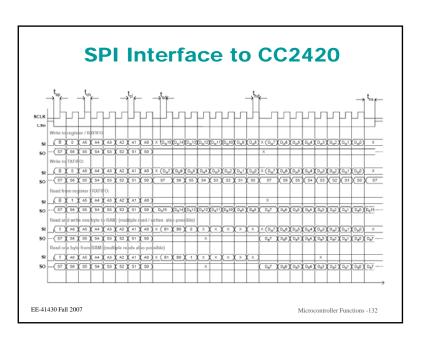

SPI Interface

Microcontroller Functions -126

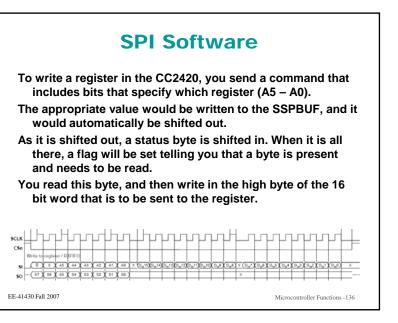

The basic idea of an SPI interface is to share information over a serial connection. It looks like the picture below. Note that the master is the source of the clock.

EE-41430 Fall 2007

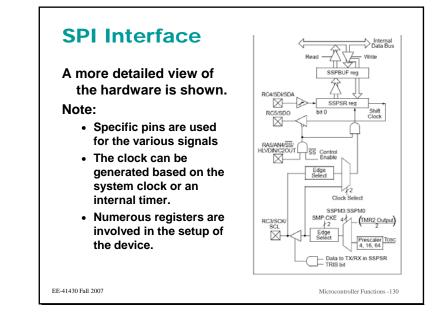

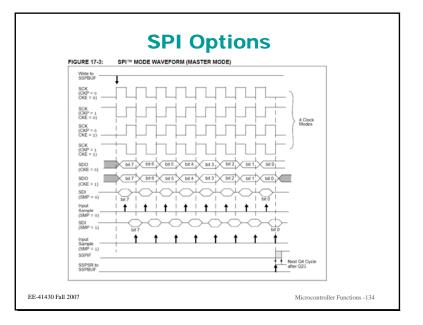

#### **SPI Interface** Basic idea: • (Master) When a byte is written into the SSPBUF and SSPSR, it gets shifted out on the SDO pin using a clock that is sent out on the SCK pin. · (Slave) If the slave is selected, it will receive the serial stream and send back one of its own (a reply) that will show up in the SSPBUF register. • (Master) Read the returning data. Data to TX/RX in SSPSR EE-41430 Fall 2007 Microcontroller Functions -131

| Name              | Bit 7                                                          | Bit 6                       | Bit 5                          | Bit 4                       | Bit 3                     | Bit 2  | Bit 1       | Bit 0       | Reset<br>Values<br>on page |

|-------------------|----------------------------------------------------------------|-----------------------------|--------------------------------|-----------------------------|---------------------------|--------|-------------|-------------|----------------------------|

| INTCON            | GIE/GIEH                                                       | PEIE/GIEL                   | TMR0IE                         | INTOIE                      | RBIE                      | TMR0IF | INTOIF      | RBIF        | 49                         |

| PIR1              | PSPIF <sup>(1)</sup>                                           | ADIF                        | RCIF                           | TXIF                        | SSPIF                     | CCP1IF | TMR2IF      | TMR1IF      | 52                         |

| PIE1              | PSPIE <sup>(1)</sup>                                           | ADIE                        | RCIE                           | TXIE                        | SSPIE                     | CCP1IE | TMR2IE      | TMR1IE      | 52                         |

| PR1               | PSPIP <sup>(1)</sup>                                           | ADIP                        | RCIP                           | TXIP                        | SSPIP                     | CCP1IP | TMR2IP      | TMR1IP      | 52                         |

| TRISA             | TRISA7(2)                                                      | TRISA6(2)                   | PORTA Da                       | ta Direction                | Control Re                | gister |             |             | 52                         |

| TRISC             | PORTC Data Direction Control Register                          |                             |                                |                             |                           |        |             | 52          |                            |

| SSPBUF            | SSP Receive Buffer/Transmit Register                           |                             |                                |                             |                           |        |             |             | 50                         |

| SSPCON1           | WCOL                                                           | SSPOV                       | SSPEN                          | CKP                         | SSPM3                     | SSPM2  | SSPM1       | SSPM0       | 50                         |

| SSPSTAT           | SMP                                                            | CKE                         | D/Ā                            | P                           | S                         | R/W    | UA          | BF          | 50                         |

| Note 1: T<br>2: F | Shaded cells<br>These bits an<br>PORTA<7:6><br>Inscillator mod | e unimpleme<br>and their di | ented on 28-<br>rection bits a | pin devices<br>are individu | and read a ally configure |        | ins based o | n various p | rimary                     |

#

# Analog to Digital Conversion

There are many sensors that measure an analog real world value and produce a signal that is a voltage or current that is proportional to the value being measured.

**Examples include:**

- Strain Gauges

- Accelerometers

- Temperature Sensors

To use these external values as part of an embedded control application, we need a way to represents the value of the analog signal inside the microcontroller.

EE-41430 Fall 2007

Microcontroller Functions -137

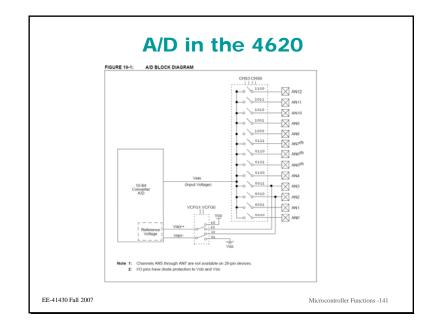

# A/D in the 4620

- The 18F4620 has a 10 bit successive approximation converter.

- The analog source can be selected from one of 13 different pins.

- There is also the capability to select different reference voltages which set the range of the analog input (maximum and minimum values.)

- As usual, there are a number of different registers associated with using the A/D converter in the device.

EE-41430 Fall 2007

Microcontroller Functions -138

| TABLE 19-2: REGISTERS ASSOCIATED WITH A/D OPERATION |                                                                                   |              |             |              |                    |         |              |        |                            |

|-----------------------------------------------------|-----------------------------------------------------------------------------------|--------------|-------------|--------------|--------------------|---------|--------------|--------|----------------------------|

| Name                                                | Bit 7                                                                             | Bit 6        | Bit 5       | Bit 4        | Bit 3              | Bit 2   | Bit 1        | Bit 0  | Reset<br>Values<br>on page |

| INTCON                                              | GIE/GIEH                                                                          | PEIE/GIEL    | TMROIE      | INTOIC       | RDIE               | TMR0IF  | INTOIL       | RBIF   | 49                         |

| PIR1                                                | PSPIF(1)                                                                          | ADIF         | RCIF        | TXIF         | SSPIF              | CCP1IF  | TMR2IF       | TMR1IF | 52                         |

| PIE1                                                | PSPIE <sup>(1)</sup>                                                              | ADIE         | RCIE        | TXIE         | SSPIE              | CCP1IE  | TMR2IE       | TMR1IE | 52                         |

| IPR1                                                | PSPIP <sup>(1)</sup>                                                              | ADIP         | RCIP        | TXIP         | SSPIP              | CCP1IP  | TMR2IP       | TMR1IP | 52                         |

| PIR2                                                | OSCFIF                                                                            | CMIF         | -           | EEIF         | BCLIF              | HLVDIF  | TMR3IF       | CCP2IF | 52                         |

| PIE2                                                | OSCFIE                                                                            | CMIE         | -           | EEIE         | BCLIE              | HLVDIE  | TMR3IE       | CCP2IE | 52                         |

| PR2                                                 | OSCEIP                                                                            | CMIP         | -           | EEIP         | BCLIP              | HLVDIP  | TMR3IP       | CCP2IP | 52                         |

| ADRESH                                              | A/D Result Register High Byte                                                     |              |             |              |                    |         |              |        |                            |

| ADRESL                                              | A/D Result Register Low Byte                                                      |              |             |              |                    |         |              |        |                            |

| ADCOND                                              | _                                                                                 | _            | CHS3        | CHS2         | CHS1               | CHS0    | GO/DONE      | ADON   | 51                         |

| ADCON1                                              | -                                                                                 | -            | VCFG1       | VCFG0        | PCFG3              | PCFG2   | PCFG1        | PCFG0  | 51                         |

| ADCON2                                              | ADFM                                                                              | -            | ACQT2       | ACQT1        | ACQT0              | ADCS2   | ADCS1        | ADCS0  | 51                         |

| PORTA                                               | RA7(1)                                                                            | RA6(1)       | RA5         | RA4          | RA3                | RA2     | RA1          | RA0    | 52                         |

| TRISA                                               | TRISA7 <sup>(2)</sup> TRISA6 <sup>(2)</sup> PORTA Data Direction Control Register |              |             |              |                    |         |              |        | 52                         |

| PORTB                                               | R87                                                                               | RB6          | RB5         | RB4          | RB3                | RB2     | RB1          | RB0    | 52                         |

| TRISB                                               | PORTB Data Direction Control Register                                             |              |             |              |                    |         |              |        | 52                         |

| ATB                                                 | PORTB Da                                                                          | ta Latch Reg | ister (Read | and Write to | Data Latch         | )       |              |        | 52                         |

| PORTE <sup>(4)</sup>                                | -                                                                                 | -            | -           | -            | RE3 <sup>(3)</sup> | RE2     | RE1          | RE0    | 52                         |

| TRISE <sup>(4)</sup>                                | IBF                                                                               | OBF          | IBOV        | PSPMODE      | -                  | TRISE2  | TRISE1       | TRISE0 | 52                         |

| LATE <sup>(4)</sup>                                 | -                                                                                 | -            | -           | -            | -                  | PORTE D | ata Latch Re | gister | 52                         |

# A/D in the 4620

#### Note:

- The analog signal must be allowed to settles before doing the conversion.

- Since it is a successive approximation converter, it is not the fastest converter in the world, and the conversion time must be chosen based on the system clock. (The device needs more cycles to convert (per bit) as the system clock speed goes up.)

- Some external signals can be used as references.

- Pins used as analog inputs must be setup as analog. (Note that analog is the default.)

EE-41430 Fall 2007